Download Code Here

-----------------------------------------------------------------------------------------------------------

Chào các bạn hôm nay mình sẽ viết 1 bài để hướng dẫn

các bạn tạo 1 Project FPGA trong Altium để nạp nào Nanoboard 3000.

1.những phần mềm cần có:

- Active HDL

- Altium

2. Viết chương trình bằng ngôn ngữ VHDL trên Active HDL (bài D3_C2 trên Blog).

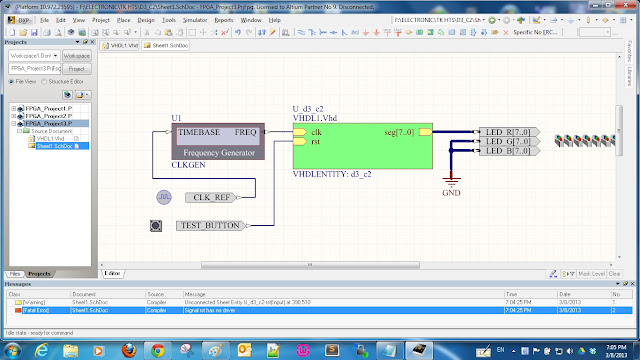

3. Vẽ mạch. ( Bài D3_C2).

3.1. Một số linh kiện cần dùng và thư viện chứa chúng.

- FPGA NB3000 Port-Plugin.IntLib

LEDS_RGB

- FPGA Instruments.IntLib

CLKGEN

- FPGA NB2DSK01 Port-Plugin.IntLib

CLOCK_REFERENCE

TEST_BUTTON

3.2. Tạo Project trong altium

- Copy code từ bên active HDL sang.

- Paste code vào file VHDL bên altium.

- Lưu file VHDL lại

---------------------------------------------------------------------------------------------------------

Chi tiết xin liên hệ:

Nguyễn Duy Tân

Email: nguyenduytan1909@gmail.com hoặc duytandhdt3k5@gmail.com

Yahoo: nguyenduytan1909

Skype: Tannd1909

FaceBook:Nguyễn Duy Tân

-----------------------------------------------------------------------------------------------------------

Chào các bạn hôm nay mình sẽ viết 1 bài để hướng dẫn

các bạn tạo 1 Project FPGA trong Altium để nạp nào Nanoboard 3000.

1.những phần mềm cần có:

- Active HDL

- Altium

2. Viết chương trình bằng ngôn ngữ VHDL trên Active HDL (bài D3_C2 trên Blog).

3. Vẽ mạch. ( Bài D3_C2).

3.1. Một số linh kiện cần dùng và thư viện chứa chúng.

- FPGA NB3000 Port-Plugin.IntLib

LEDS_RGB

- FPGA Instruments.IntLib

CLKGEN

- FPGA NB2DSK01 Port-Plugin.IntLib

CLOCK_REFERENCE

TEST_BUTTON

3.2. Tạo Project trong altium

- Lưu Project vào máy.

- Add thêm File VHDL

- Paste code vào file VHDL bên altium.

- Lưu file VHDL lại

- Biên dịch và sửa lỗi code VHDL

- Tạo file sơ đồ nguyên lý mạch.

- Lưu sơ đồ nguyên lý lại.

- Lấy linh kiện mới tạo ra bằng code VHDL

- Chọn linh kiện vừa tạo và nhấn OK ta sẽ có kinh kiện.

- Linh kiện đã được đặt trong sơ đồ nguyên lý.

- Lấy LEDS_RGB 3 màu trong thư viện của Nanoboard 3000.

- Lấy CLKGEN ( bộ này để chỉnh xung nhịp khi kết nối với nanoboard 3000)

- CLOCK_REFERENCE lấy xung CLOCK.

- Lấy BUTTON để làm nút RESET

- Mạch vẽ xong!

- Kiểm tra sơ đồ nguyên lý và lưu lại lần nữa.

- Kiểm tra Project xem có lỗi không! nếu không có lỗi ta chuyển sang giai đoạn kết nối với Nanoboard 3000.

Các bạn có thể xem video hướng dẫn ở dưới!

Chi tiết xin liên hệ:

Nguyễn Duy Tân

Email: nguyenduytan1909@gmail.com hoặc duytandhdt3k5@gmail.com

Yahoo: nguyenduytan1909

Skype: Tannd1909

FaceBook:Nguyễn Duy Tân